M.S. Candidate: Salih Atabey

Program: Information Systems

Date: 08.07.2025 / 10:00

Place: B-116

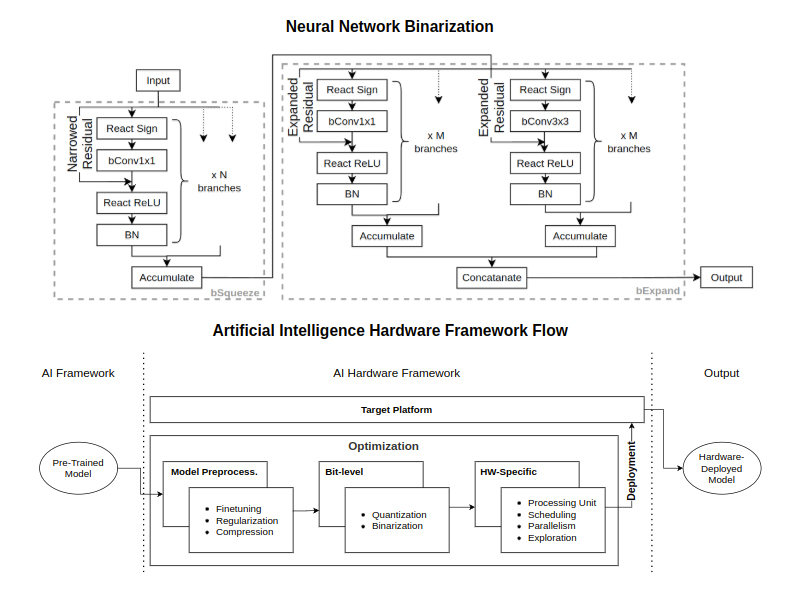

Abstract: In embedded and edge computing systems where real-time performance and energy consumption are critical, binary neural networks are becoming more and more relevant. Computational complexity and memory requirements are much lower with binarization, a strong compression method that lowers network weights and activations to binary values. However, this compression often leads to information loss, impacting model accuracy. This study examines advanced binarization methods and applies them to lightweight architectures such as SqueezeNet, which has not been previously binarized. A binarized version of SqueezeNet is proposed and optimized with architectural enhancements. A comprehensive survey of artificial intelligence hardware frameworks for FPGAs are presented by categorizing and evaluating existing platforms based on design philosophy, optimization strategies, and deployment compatibility. Particular emphasis is placed on two frameworks, FINN and HLS4ML, which are explored in detail to implement binarized neural networks on FPGA platforms. The study evaluates performance trade-offs and implementation challenges using datasets of varying complexity, including MNIST, CIFAR-10, and ImageNet. Comparative analysis of full-precision and binarized models highlights the impact of architecture and hardware framework choices on accuracy, resource efficiency, and performance. While practical deployment outcomes provide valuable insights, this study emphasizes architectural and hardware-level considerations critical for practical binary neural network applications in constrained embedded systems.